**Preliminary Data Book**

# FEATURES

#### Single chip Super VGA LCD controlle r

- Pin compatible with CL-GD7542 - IBM<sup>®</sup> VGA hardware-compatible

## GUI acceleration

- BitBLT (bit block transfer) engin e

- Color expansion for 8- or 16-bit pixel s

- True packed-pixel addressing for 8 and 16 bp p

- Programmable linear memory addressin g

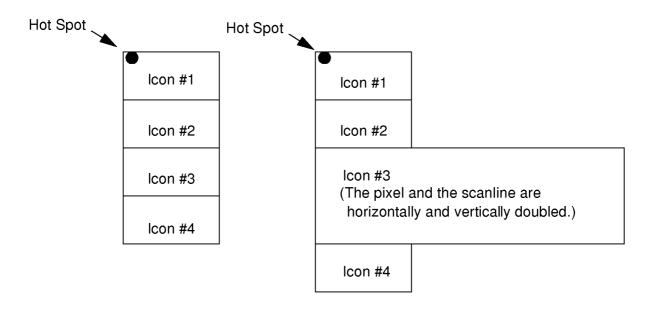

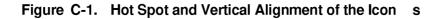

- 32  $\times$  32 or 64  $\times$  64 hardware curso r

#### Multimedia acceleration and enhancemen t

- 8-bit feature connector port for video overla y

- Interface to analog encoders for NTSC/PAL-ou t

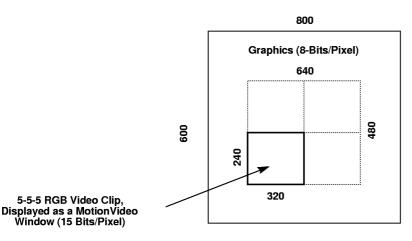

- MVA™ (MotionVideo™ Acceleration) *CL-GD7543 only*

- True-color, full-motion video playbac k

- Multi-format frame buffer

- Integrated YCrCb: RGB color space converte r

- 2× horizontal/vertical hardware scalin g

#### ■ 32-bit direct-connect CPU host bus interface s

- '486 CPU local bus (up to 50 MHz @ 5 V )

- VESA® VL-Bus™

- PCI system bus with burst support: big-endian byteorder hardware support for PowerP C<sup>™</sup>

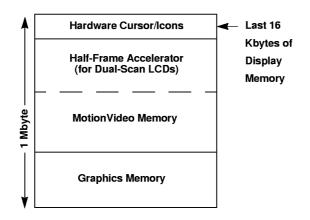

#### Scalable 1- and 2-Mbyte display memor y

- Two or four 256K × 16 DRAMs, or four 512K × 8 DRAMs

- Extended-Data-Out/Hyper-Page-Mode DRAM suppor t

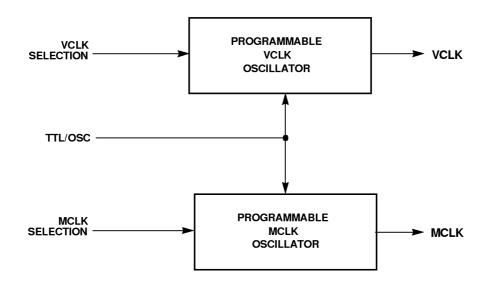

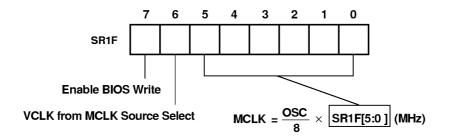

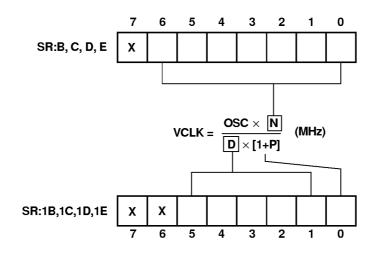

#### Integrated programmable frequency synthesize r

- Core VCLK up to 80 MHz @ 5 V; 77 MHz @ 3.3 V

- Core MCLK up to 60 MHz @ 5 V; 50 MHz @ 3.3 V

- Vertical refresh rates up to 75 Hz (depending on the graphics mode, MCLK, and voltage level of core VCC)

## GUI-Accelerated SVGA LCD Controller for Portable Computer s

- 64 × 64 pixel size hardware pop-up icon s

- Displays up to four independently controlled, 4-color icon s

- Integrated 24-bit true-color RAMDAC

- 640 × 480 non-interlaced, 16M colors (CL-GD7543 only)

- 800 × 600 non-interlaced, 64K colors

- 1024  $\times$  768 non-interlaced, 256 colors

- 1280 × 1024 interlaced, 256 color s

- Support for 640 × 480 and 800 × 600 LCDs

- Dual-scan color and monochrome STN LCD s

- Color TFT LCDs (9-, 12-, 18-, and 24-bit interfaces)

- Dithering algorithm automatically adds up to 6 bits per primary color without decreasing spatial resolutio n

- Enhanced frame-rate modulation algorithm improves display quality with fast-response STN LCDs (~100 ms )

- SimulSCAN™ (simultaneous CRT and LCD )

- Full-screen VGA support on 800  $\times$  600 LCDs

#### Power-management capabilitie s

- 3.3-V, 5.0-V, and mixed-voltage operatio n

- Hardware-suspend input pin or software-suspend optio n

- Self-refresh DRAMs or DRAM refresh via 32-kHz cloc k

- Internal timers for Standby mode and backlight contro 1

- LCD power sequencing

- VESA® DPMS (Display Power Management Signaling)

- DDC-1 (Display Data Channel) suppor t

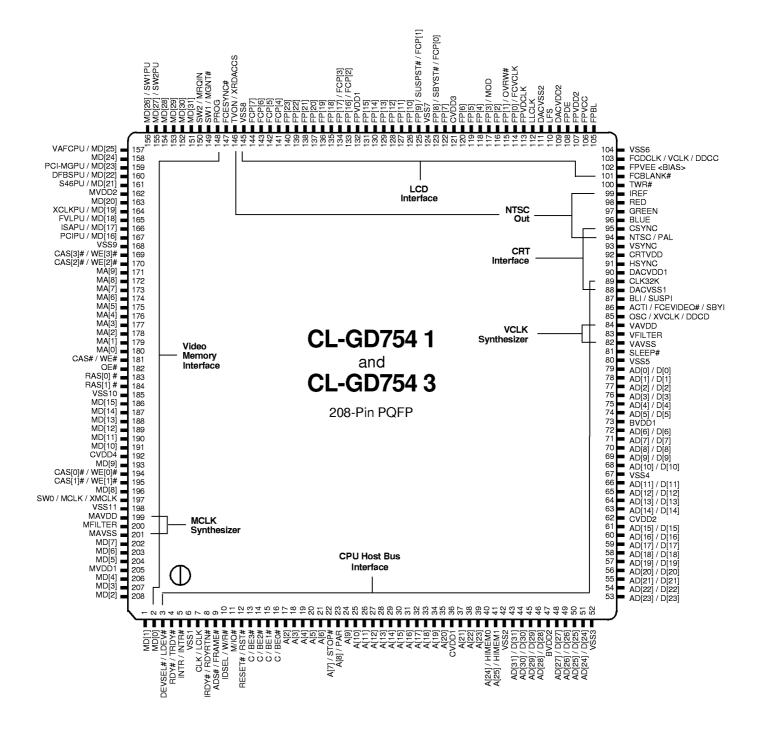

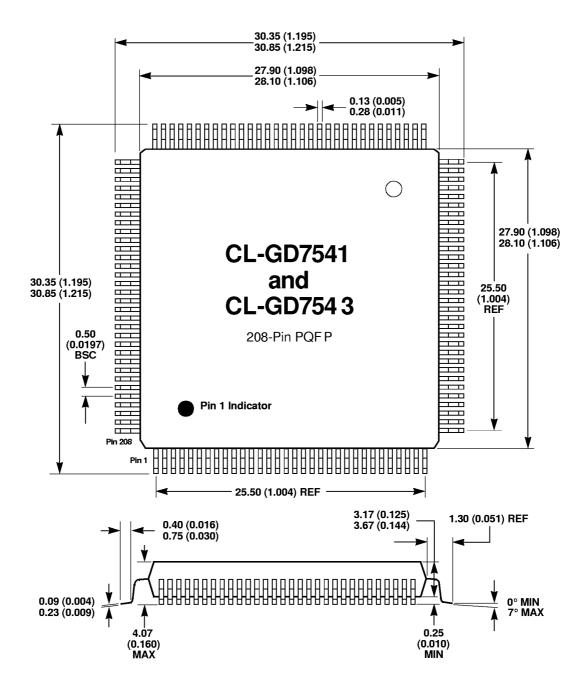

- EIAJ standard 208-pin quad flat packag e

## **OVERVIEW**

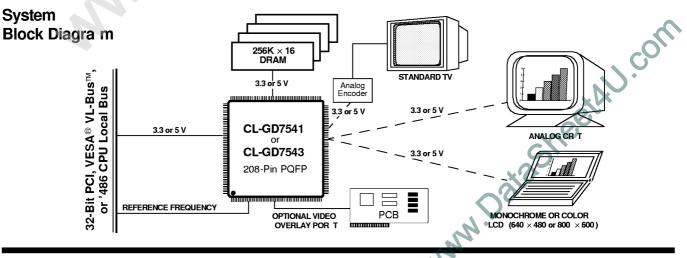

The GUI-accelerated SVGA LCD controllers — CL-GD7541 and CL-GD7543 — are the latest members of the pin compatible CL-GD754X family. They provide the performance and int egration required for the next generation of mid-range to premium portable computers.

The CL-GD7541/GD7543 uses Cirrus Logic's advanced 0.6-  $\mu m$  CMOS process to provide improved 3.3-V operation and support for 1024  $\times$  768 CRT refresh rates of 70 Hz. In addition, increased performance can be achieved through the use of high-speed Extended-Data-Out (EDO) / Hyper-Page-Mode DRAMs. A complete graphics subsystem can be built using only three active components: the CL-GD7541/GD7543 and two DRAMs.

## **UNIQUE FEATURE S**

#### Design Flexibility

- Pin-compatible with CL-GD7542

- Big-endian byte ordering in display memory with PCI host interface

#### High Performance

- BitBLT engine, color expansion, hardware cursor, linear addressing, and 32-bit memory interfac e

- 32-bit local bus interface, operating at up to 33 MHz, includes support for PCI with burst mod e

- Hardware 'pop-up' icon s

#### Multimedia

- 8-bit dynamic Feature Connector port

- Interface to NTSC/PAL analog encoders

- Drivers supplied for 3D-graphics libraries and emerging APIs (advanced programming interface) for game s

#### MVA™ (CL-GD7543 only)

- MVA<sup>TM</sup> (MotionVideo<sup>TM</sup> Acceleration)

- Multi-format frame buffer and YCrCb-to-RGB color space conversion

- 2× hardware scaling for playbac k

#### Enhanced LCD Support

- 800 × 600 LCD support (both TFT and dual-scan STN) with comprehensive resolution-compensation suppor t

- Enhanced frame-rate modulatio n

- Intelligent dithering algorithm expands the number of bits per primary color (RGB) on TFT or STN LCD s

#### **Power Management**

- 3.3-V, 5.0-V, or mixed-voltage suppor t

- Hardware-initiated Standby and Suspend modes and VESA<sup>®</sup> DPMS support for CRTs

Both the CL-GD7541 and CL-GD7543 provide the following CL-GD7542 features: BitBLT GUI acceleration, true-color cap ability, support for 800  $\times$  600 LCDs, and mixed-voltage operation for low power consumption.

The CL-GD7543 fully supports all features of the CL-GD7542, including MotionVide o<sup>™</sup> Acceleration (MVA<sup>™</sup>) for playback of Video for Windows .AVI (audio-video interleaved) files .

For the cost-sensitive value market, the CL-GD7541 provides most of the performance and features of the CL-GD7543, including TV-out, Feature Connector, 3D game acceleration, and 2-Mbyte display memory. However, the CL-GD7541 does not support the MVA hardware playback enhancements, relying instead upon standard primary surface DCI support.

# BENEFITS

- □ CL-GD754X family offers products for a wide range of market segments. Design knowledge gained with any CL-GD754X device can be leveraged over entire CL-GD754X family.

- □ Supports 'X86 designs with little-endian data; supports PowerPC<sup>™</sup> designs with big-endian data .

- □ Accelerates GUIs such as Microsof t<sup>®</sup> Windows<sup>®</sup>; provides high resolution and color-depth capabilities .

- □ Increases system throughput; PCI interface allows use in 'X86, PowerPC<sup>™</sup>, or other platforms .

- Provides hot-key display for on-screen symbols such as battery 'fuel gauge' and contrast/brightness controls.

- □ Allows overlay capability for live 'TV in a window' .

- □ Integrated design can be developed to display computergenerated data on a TV or to record to a VCR .

- Supports emerging standards for DOS and Window s<sup>®</sup>based 3D applications.

- □ Hardware enhancement for playback of Video for Windows .AVI files .

- Displays separate graphics and video windows at independent color depths.

- Enlarges video clips with little or no frame-rate reduction .

- Supports latest LCD technology and enables full use of the display area whether in graphics or text mode.

- Improves display quality; increases stability of shades .

- Displays high- and true-color modes with smooth shading (no contouring) on all supported LCD types.

- □ Minimizes operating power consumption; provides manufacturing flexibility.

- Reduces power consumption; supports Energy Star monitors for 'green PC' compliance .

February 1995

## SOFTWARE SUPPOR T

#### **Operating System and Application Software Driver s**

| Software Driver s <sup>a</sup>                               | Resolution Supporte d                                                                                                          | Number of Color s                                     |

|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| Microsoft®/Intel® DCI™ (Display<br>Control Interface)        | $\begin{array}{c} 640 \times 480,800 \times 600,1024 \times 768,1280 \times 1024 \\ 640 \times 480,800 \times 600 \end{array}$ | 256<br>65,536                                         |

| Microsoft <sup>®</sup> Windows <sup>®</sup> v3.1             | $640 \times 480,800 \times 600,1024 \times 768,1280 \times 1024$ $640 \times 480,800 \times 600$ $640 \times 480$              | 256<br>65,536<br>16.8 million (CL-GD7543 only)        |

| Microsoft® Windows NT™ v3.1                                  | 640 × 480, 800 × 600, 1024 × 768                                                                                               | 16 and 256                                            |

| OS/2 <sup>®</sup> v2.0, v2.1                                 | 640 × 480, 800 × 600, 1024 × 768<br>640 × 480, 800 × 600<br>640 × 480                                                          | 16 and 256<br>65,536<br>16.8 million (CL-GD7543 only) |

| AutoCAD® v11, v12                                            | 640 × 480, 800 × 600, 1024 × 768<br>640 × 480, 800 × 600<br>640 × 480                                                          | 16 and 256<br>65,536<br>16.8 million (CL-GD7543 only) |

| Autoshade <sup>®</sup> v2.0<br>3D Studio <sup>®</sup> v1, v2 | 640 × 480, 800 × 600, 1024 × 768<br>640 × 480, 800 × 600<br>640 × 480                                                          | 256<br>65,536<br>16.8 million (CL-GD7543 only)        |

<sup>a</sup> Driver support for additional applications is provided by independent software vendors, either with specific drivers or through VESA mode support. In many instances, existing drivers for the CL-GD542X can be used with the CL-GD7541/GD7543. For more information concerning driver support, contact the software manufacturer.

#### BIOS

| Feature                                                                                                                                                                                                                                  | Benefit                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Available as 48-Kbyte BIOS to provide<br>optimum performance with VGA and VES A <sup>®</sup><br>extended mode support, or as a 32-Kbyte<br>subset with a 16-Kbyte-relocatable module or<br>loaded as TSRs (terminate and stay resident ) | Provides system design options for the best combination of performance and functionality.            |

| ■ Fully IBM <sup>®</sup> VGA-compatible BIOS                                                                                                                                                                                             | $\hfill\square$ Ensures compatibility with the existing base of PC applications $\hfill$ .           |

| <ul> <li>VESA<sup>®</sup> VBE (VGA BIOS extensions) 1.2 and<br/>PM (power management) suppor t</li> </ul>                                                                                                                                | Compatible with industry standard for extended mode support beyond VGA and power-management control. |

#### Software Utilities

| Utility                  | Function                                                                                                                                                                                                               |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AutoResolution Switching | Windows <sup>®</sup> application for automatically switching display resolutions (for example, from a 1024 $\times$ 768 CRT to lower-resolution 640 $\times$ 480 or 800 $\times$ 600 LCDs) without relaunching Windows |

| CLDemo                   | Demonstration program to test various capabilities of the CL-GD7541/GD7543                                                                                                                                             |

| CLMode                   | Video mode and video display configuration utility suitable for end-use distribution (includes foreign language translations)                                                                                          |

| OEMSI                    | BIOS-customization utility for OEM development us e                                                                                                                                                                    |

| PCLRegs                  | VGA controller register viewer/editor for OEM development us e                                                                                                                                                         |

| Switcher                 | Video configuration TSR (terminate and stay resident)                                                                                                                                                                  |

| WinMode                  | Windows $^{\textcircled{B}}$ application for graphics mode and display type configuration (includes foreign language translations, selectable from within the utility )                                                |

# TABLE OF CONTENT S

| 1. | <b>PIN INI</b> | FORM ATION                                                                                                     | 15   |

|----|----------------|----------------------------------------------------------------------------------------------------------------|------|

|    | 1.1            | Pin Diagram                                                                                                    | 15   |

|    | 1.2            | Pin Tables                                                                                                     | 16   |

|    | 1.3            | Block Diagrams: CL-GD7541/GD7543 Interfaces                                                                    | . 20 |

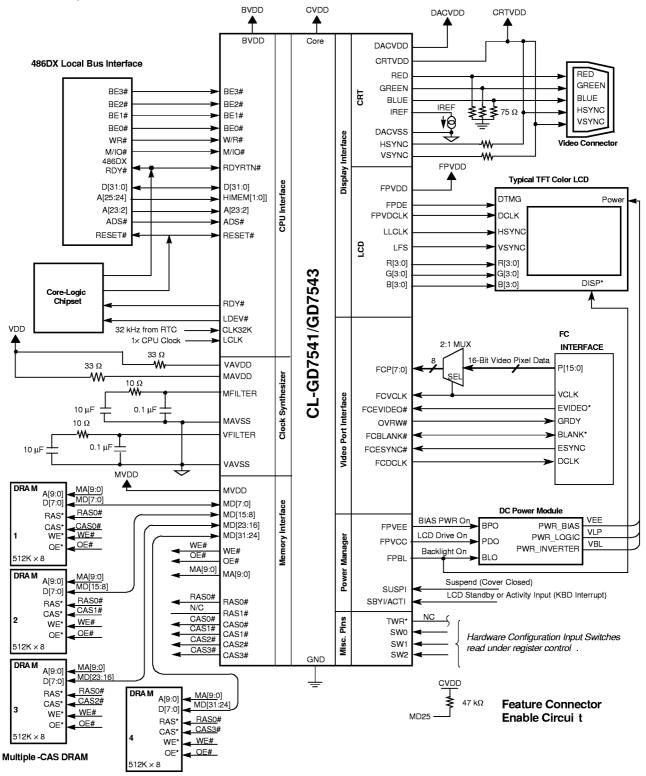

|    | 1.3.1          | Local Bus (32-Bit '486DX or VES A <sup>®</sup> VL-Bus™), 2-Mbyte 512K × 8 DRAM, 12-Bit TFT Color, Video Port   | 20   |

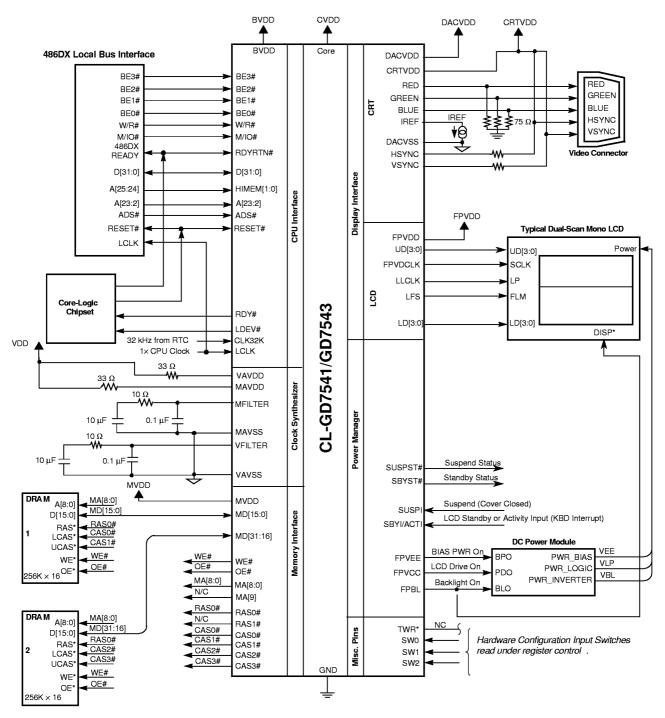

|    | 1.3.2          | Local Bus (32-Bit '486DX or VES A <sup>®</sup> VL-Bus™), 1-Mbyte 256K × 16 DRAM,<br>8-Bit Dual-Scan Monochrome | . 21 |

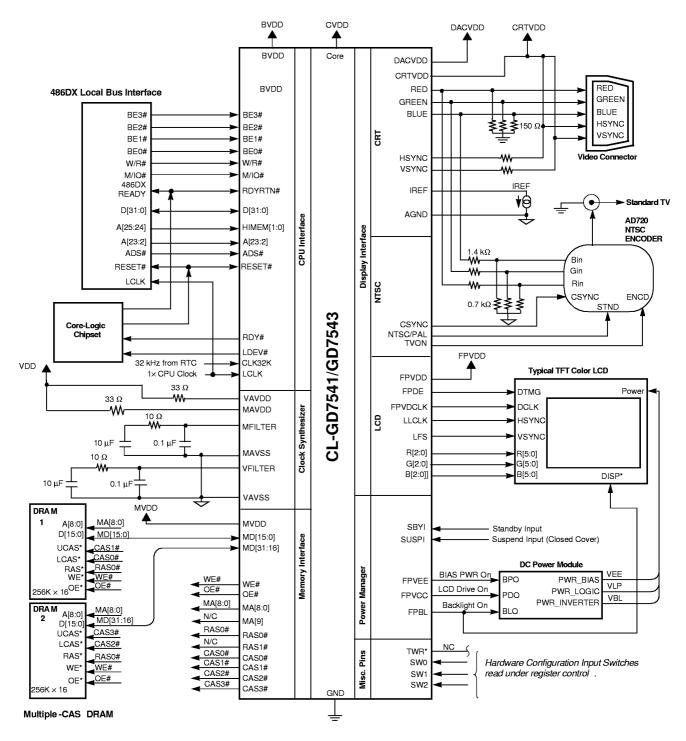

|    | 1.3.3          | Local Bus (32-Bit '486DX or VES A <sup>®</sup> VL-Bus™), 1-Mbyte 256K × 16 DRAM, 18-Bit TFT Color, NTSC Output | . 22 |

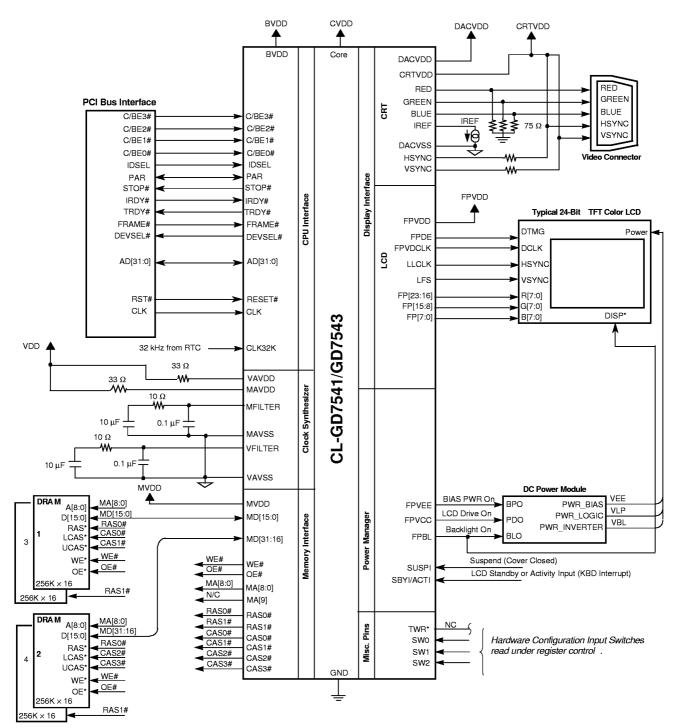

|    | 1.3.4          | PCI Bus, 2-Mbyte 256K × 16 DRAM, 24-Bit TFT Color                                                              | . 23 |

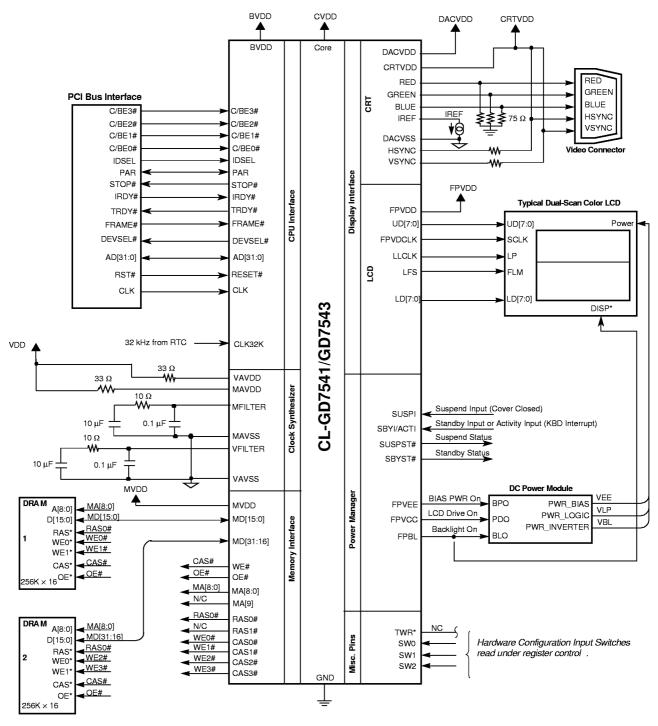

|    | 1.3.5          | PCI Bus, 1-Mbyte 256K × 16 DRAM, 16-Bit Dual-Scan Color                                                        | . 24 |

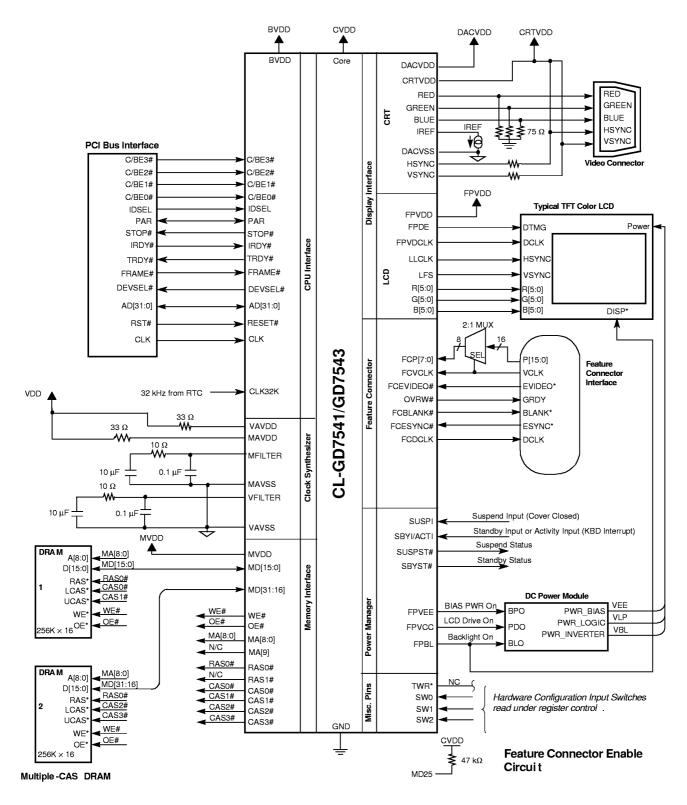

|    | 1.3.6          | PCI Bus, 1-Mbyte 256K × 16 DRAM, 18-Bit TFT Color,<br>Feature Connector Interface                              | 25   |

| 2. | PIN DE         | ESCRIPTIONS                                                                                                    | 27   |

|    | 2.1            | CPU Host Bus Interface Pins                                                                                    | 28   |

|    | 2.1.1          | CL-GD7541/GD7543 CPU Host Bus Interface Pins to<br>'486 or VESA <sup>®</sup> VL-Bus™ Local Bus                 | 28   |

|    | 2.1.2          | CL-GD7541/GD7543 CPU Host Bus Interface Pins to PCI Bus                                                        |      |

|    | 2.2            | LCD Interface Pins                                                                                             |      |

|    | 2.3            | CRT Interface Pins                                                                                             |      |

|    | 2.4            | NTSC and PAL Interface Pins                                                                                    | 43   |

|    | 2.5            | Dual-Frequency Synthesizer Interface Pins                                                                      | . 45 |

|    | 2.6            | Display Memory Interface Pins                                                                                  | . 47 |

|    | 2.7            | Configuration Input Pins                                                                                       | 48   |

|    | 2.8            | Switch and Miscellaneous Configuration Input P ins                                                             | . 50 |

|    | 2.9            | Feature Connector Pins                                                                                         | 51   |

|    | 2.10           | Power Management Pins                                                                                          |      |

|    | 2.11           | Ground Pins                                                                                                    | 55   |

|    | 2.12           | Power Pins                                                                                                     | 56   |

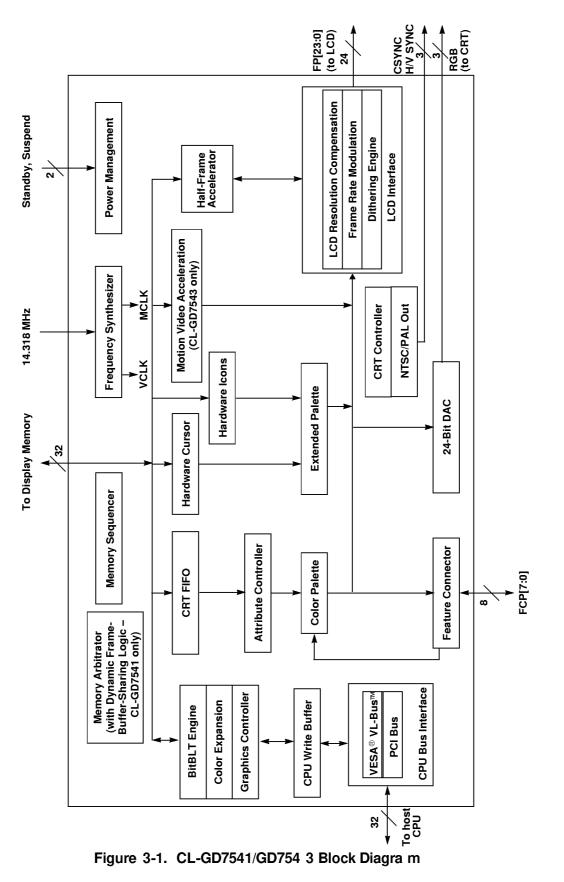

| 3. | FUNCT          | TIONAL DESCRIPTION                                                                                             | 59   |

|    | 3.1            | Introduction                                                                                                   | 59   |

|    | 3.2            | Functional Blocks                                                                                              | 59   |

|    | 3.2.1          | CPU Bus Interface                                                                                              | 59   |

|    | 3.2.2          | CPU Write Buffer                                                                                               | 61   |

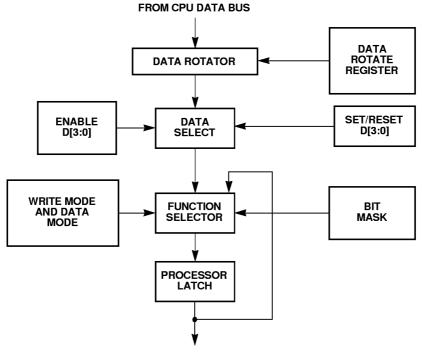

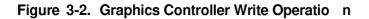

|    | 3.2.3          | Graphics Controller                                                                                            | 61   |

|    | 3.2.4          | Color Expansion                                                                                                |      |

|    | 3.2.5          | Bit Block Transfer (BitBLT) Engine                                                                             |      |

|    | 3.2.6          | Memory Arbitrator                                                                                              |      |

|    | 3.2.7          | Memory Sequencer                                                                                               |      |

|    | 3.2.8          | Dynamic Frame-Buffer-Sharing Logic (CL-GD7541 Only)                                                            |      |

|    | 3.2.9          | CRT FIFO                                                                                                       |      |

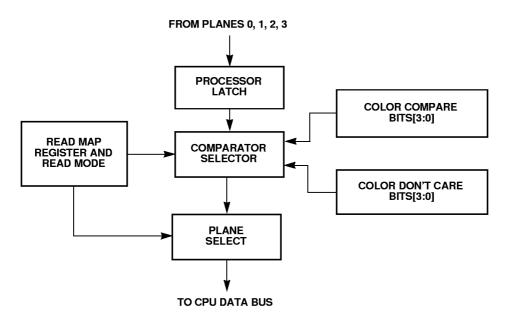

|    | 3.2.10         | Attribute Controller                                                                                           |      |

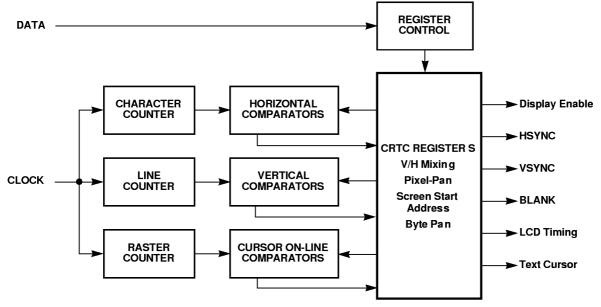

|    | 3.2.11         | CRT Controller                                                                                                 |      |

|    | 3.2.12         | Hardware Cursor                                                                                                | 67   |

|    | 3.2.13 | Hardware Pop-up Icons                                      | 67  |

|----|--------|------------------------------------------------------------|-----|

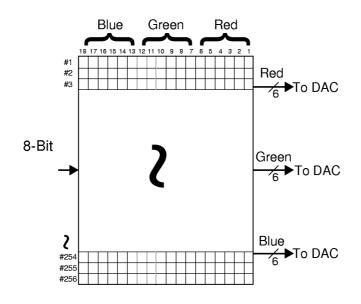

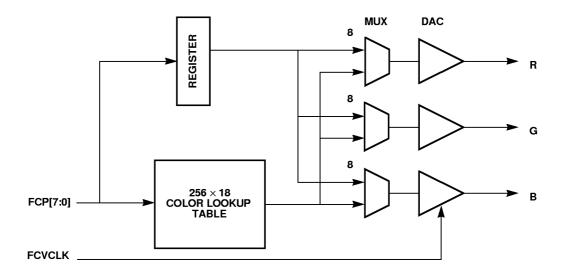

|    | 3.2.14 | Color Palette                                              | 68  |

|    | 3.2.15 | Extended Palette RAM                                       | 71  |

|    | 3.2.16 | Triple DAC                                                 | 71  |

|    | 3.2.17 | MotionVideo™ Acceleration (CL-GD7543 Only)                 | 72  |

|    | 3.2.18 | Feature Connector                                          | 79  |

|    | 3.2.19 | NTSC/PAL Out                                               | 79  |

|    | 3.2.20 | Half-Frame Accelerator                                     | 80  |

|    | 3.2.21 | LCD Interface                                              | 80  |

|    | 3.2.22 | LCD Resolution Compensation                                | 80  |

|    | 3.2.23 | Frame Rate Modulation                                      | 83  |

|    | 3.2.24 | Dithering Engine                                           | 84  |

|    | 3.2.25 | Frequency Synthesizer                                      | 89  |

|    | 3.2.26 | Power Management                                           | 90  |

|    | 3.3    | Performance                                                | 91  |

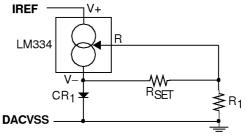

|    | 3.4    | RAMDAC Operation                                           |     |

|    | 3.4.1  | Writing to the Color Lookup Table (CLUT)                   | 91  |

|    | 3.4.2  | Reading from the CLUT                                      | 92  |

|    | 3.5    | Programmable Core Voltage                                  | 92  |

|    | 3.5.1  | 3.3-V Core Voltage                                         | 92  |

|    | 3.5.2  | 5.0-V Core Voltage                                         | 92  |

|    | 3.6    | Compatibility                                              | 92  |

|    | 3.7    | Extension Registers                                        | 93  |

|    | 3.8    | Testability                                                | 93  |

|    | 3.9    | Configuration Inputs                                       | 93  |

|    | 3.9.1  | Hardware Configuration Inputs                              | 93  |

|    | 3.9.2  | Software Configuration Inputs                              | 94  |

|    | 3.10   | Software Support                                           |     |

|    | 3.10.1 | Software Support for OEMs                                  | 95  |

|    | 3.10.2 | Software Support for End Users                             | 95  |

|    | 3.11   | Package                                                    |     |

| 4. | MODE   | TABLES                                                     | 97  |

|    | 4.1    | CRT-Only Mode Tables                                       |     |

|    | 4.1.1  | IBM <sup>®</sup> Standard VGA CRT-Only Modes               |     |

|    | 4.1.2  | Cirrus Logic Extended CRT-Only Modes                       |     |

|    | 4.2    | LCD-Only/SimulSCAN™ Mode Tables                            |     |

|    | 4.2.1  | Cirrus Logic LCD-Only/SimulSCAN™ Modes for 800 x 600 LCDs  |     |

|    | 4.2.2  | Cirrus Logic LCD-Only/SimulSCA N™ Modes for 640 x 480 LCDs |     |

| -  |        | • •                                                        |     |

| 5. | VGA R  | EGISTER PORT MAP                                           | 103 |

| 6. | REGIS  | TER SUMMARY                                                | 105 |

|    | 6.1    | Summary of External/General Registers in Chapter 7         | 105 |

|    | 6.2    | Summary of Sequencer Registers in Chapter 8                |     |

|    | 6.3    | Summary of CRT Controller Registers in Chapter 9           |     |

|    | 6.4    | Summary of Graphics Controller Registers in Chapter 10     |     |

|    | 6.5    | Summary of Attribute Controller Registers in Chapter 11    |     |

|    | 6.6    | Summary of Extension Registers in Chapter 12               |     |

|    |        | -                                                          |     |

| 7. | EXTER                                                                                                                                               | NAL/GENERAL REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 113                                                                                                                                                                                                                                                                            |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 7.1                                                                                                                                                 | MISC: Miscellaneous Output Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 113                                                                                                                                                                                                                                                                          |

|    | 7.2                                                                                                                                                 | FC: Feature Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                |

|    | 7.3                                                                                                                                                 | FEAT: Input Status Register 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                |

|    | 7.4                                                                                                                                                 | STAT: Input Status Register 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                |

|    | 7.5                                                                                                                                                 | 3C3: Sleep Mode Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                |

|    | 7.6                                                                                                                                                 | 3C6: Pixel Mask Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                |

|    | 7.7                                                                                                                                                 | 3C7: Pixel Address Read Mode Register (Write Only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                |

|    | 7.8                                                                                                                                                 | 3C7: DAC State Register (Read Only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                |

|    | 7.9                                                                                                                                                 | 3C8: Pixel Address Write Mode Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                |

|    | 7.10                                                                                                                                                | 3C9: Pixel Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                |

|    | 7.11                                                                                                                                                | PCI00: PCI Device ID / PCI Vendor ID Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 125                                                                                                                                                                                                                                                                          |

|    | 7.12                                                                                                                                                | PCI04: PCI Command Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                |

|    | 7.13                                                                                                                                                | PCI04: PCI Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 127                                                                                                                                                                                                                                                                            |

|    | 7.14                                                                                                                                                | PCI10: PCI Base Address Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                |

|    | 7.15                                                                                                                                                | PCI3C: PCI Interrupt Pin and PCI Interrupt Line Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 129                                                                                                                                                                                                                                                                          |

|    | 7.16                                                                                                                                                | 46E8: Alternate Sleep Mode Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 130                                                                                                                                                                                                                                                                          |

| 8. | SEQUE                                                                                                                                               | ENCER REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 131                                                                                                                                                                                                                                                                            |

| •  | 8.1                                                                                                                                                 | SRX: Sequencer Index Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                |

|    | 8.2                                                                                                                                                 | SR0: Reset Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                |

|    | 8.3                                                                                                                                                 | SR1: Clocking Mode Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                |

|    | 8.4                                                                                                                                                 | SR2: Plane Mask Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                |

|    | 8.5                                                                                                                                                 | SR3: Character Map Set Select Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                |

|    | 8.6                                                                                                                                                 | SR4: Memory Mode Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                |

|    |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                |

| 9. | CRT C                                                                                                                                               | ONTROLLER REGISTE RS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 141                                                                                                                                                                                                                                                                            |

| 9. | <b>CRT C</b><br>9.1                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                |

| 9. |                                                                                                                                                     | CRX: CRT Controller Index Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 141                                                                                                                                                                                                                                                                          |

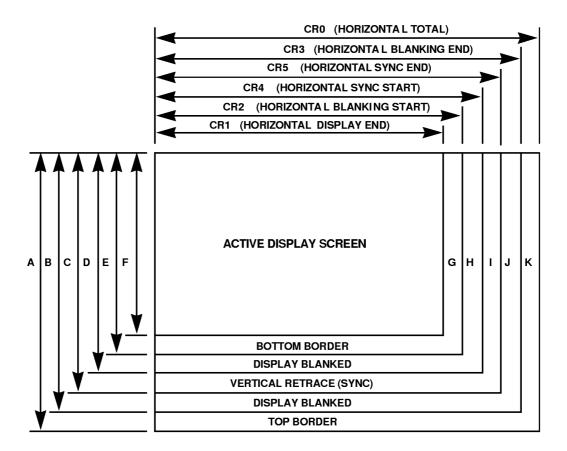

| 9. | 9.1                                                                                                                                                 | CRX: CRT Controller Index Register<br>CR0: Horizontal Total Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 141<br>. 142                                                                                                                                                                                                                                                                 |

| 9. | 9.1<br>9.2                                                                                                                                          | CRX: CRT Controller Index Register<br>CR0: Horizontal Total Register<br>CR1: Horizontal Display End Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 141<br>. 142<br>. 145                                                                                                                                                                                                                                                        |

| 9. | 9.1<br>9.2<br>9.3                                                                                                                                   | CRX: CRT Controller Index Register<br>CR0: Horizontal Total Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 141<br>. 142<br>. 145<br>. 146                                                                                                                                                                                                                                               |

| 9. | 9.1<br>9.2<br>9.3<br>9.4                                                                                                                            | CRX: CRT Controller Index Register<br>CR0: Horizontal Total Register<br>CR1: Horizontal Display End Register<br>CR2: Horizontal Blanking Start Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 141<br>. 142<br>. 145<br>. 146<br>. 147                                                                                                                                                                                                                                      |

| 9. | 9.1<br>9.2<br>9.3<br>9.4<br>9.5                                                                                                                     | CRX: CRT Controller Index Register<br>CR0: Horizontal Total Register<br>CR1: Horizontal Display End Register<br>CR2: Horizontal Blanking Start Register<br>CR3: Horizontal Blanking End Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 141<br>. 142<br>. 145<br>. 146<br>. 147<br>. 149                                                                                                                                                                                                                             |

| 9. | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6                                                                                                              | CRX: CRT Controller Index Register<br>CR0: Horizontal Total Register<br>CR1: Horizontal Display End Register<br>CR2: Horizontal Blanking Start Register<br>CR3: Horizontal Blanking End Register<br>CR4: Horizontal Sync Start Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 141<br>. 142<br>. 145<br>. 146<br>. 147<br>. 149<br>. 150                                                                                                                                                                                                                    |

| 9. | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7                                                                                                       | CRX: CRT Controller Index Register<br>CR0: Horizontal Total Register<br>CR1: Horizontal Display End Register<br>CR2: Horizontal Blanking Start Register<br>CR3: Horizontal Blanking End Register<br>CR4: Horizontal Sync Start Register<br>CR5: Horizontal Sync End Register<br>CR6: Vertical Total Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 141<br>. 142<br>. 145<br>. 146<br>. 147<br>. 149<br>. 150                                                                                                                                                                                                                    |

| 9. | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8                                                                                                | CRX: CRT Controller Index Register<br>CR0: Horizontal Total Register<br>CR1: Horizontal Display End Register<br>CR2: Horizontal Blanking Start Register<br>CR3: Horizontal Blanking End Register<br>CR4: Horizontal Sync Start Register<br>CR5: Horizontal Sync End Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 141<br>. 142<br>. 145<br>. 146<br>. 147<br>. 149<br>. 150<br>. 152<br>. 153                                                                                                                                                                                                  |

| 9. | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br>9.9                                                                                         | CRX: CRT Controller Index Register<br>CR0: Horizontal Total Register<br>CR1: Horizontal Display End Register<br>CR2: Horizontal Blanking Start Register<br>CR3: Horizontal Blanking End Register<br>CR4: Horizontal Sync Start Register<br>CR5: Horizontal Sync End Register<br>CR6: Vertical Total Register<br>CR7: Overflow Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 141<br>. 142<br>. 145<br>. 146<br>. 147<br>. 149<br>. 150<br>. 152<br>. 153<br>. 154                                                                                                                                                                                         |

| 9. | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br>9.9<br>9.9<br>9.10                                                                          | CRX: CRT Controller Index Register<br>CR0: Horizontal Total Register<br>CR1: Horizontal Display End Register<br>CR2: Horizontal Blanking Start Register<br>CR3: Horizontal Blanking End Register<br>CR4: Horizontal Sync Start Register<br>CR5: Horizontal Sync End Register<br>CR6: Vertical Total Register<br>CR7: Overflow Register<br>CR8: Screen A Preset Row Scan Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 141<br>142<br>145<br>146<br>147<br>149<br>150<br>152<br>153<br>154<br>155                                                                                                                                                                                                      |

| 9. | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br>9.9<br>9.10<br>9.11                                                                         | CRX: CRT Controller Index Register<br>CR0: Horizontal Total Register<br>CR1: Horizontal Display End Register<br>CR2: Horizontal Blanking Start Register<br>CR3: Horizontal Blanking End Register<br>CR4: Horizontal Sync Start Register<br>CR5: Horizontal Sync End Register<br>CR6: Vertical Total Register<br>CR7: Overflow Register<br>CR8: Screen A Preset Row Scan Register<br>CR9: Character Cell Height Register<br>CRA: Text Cursor Start Register                                                                                                                                                                                                                                                                                                                                                                                                 | 141<br>142<br>145<br>146<br>147<br>149<br>150<br>152<br>153<br>154<br>155<br>156                                                                                                                                                                                               |

| 9. | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br>9.9<br>9.10<br>9.11<br>9.12                                                                 | CRX: CRT Controller Index Register<br>CR0: Horizontal Total Register<br>CR1: Horizontal Display End Register<br>CR2: Horizontal Blanking Start Register<br>CR3: Horizontal Blanking End Register<br>CR4: Horizontal Sync Start Register<br>CR5: Horizontal Sync End Register<br>CR6: Vertical Total Register<br>CR7: Overflow Register<br>CR8: Screen A Preset Row Scan Register<br>CR9: Character Cell Height Register                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 141<br>. 142<br>. 145<br>. 146<br>. 147<br>. 149<br>. 150<br>. 152<br>. 153<br>. 154<br>. 155<br>. 156<br>. 157                                                                                                                                                              |

| 9. | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br>9.9<br>9.10<br>9.11<br>9.12<br>9.13                                                         | CRX: CRT Controller Index Register<br>CR0: Horizontal Total Register<br>CR1: Horizontal Display End Register<br>CR2: Horizontal Blanking Start Register<br>CR3: Horizontal Blanking End Register<br>CR4: Horizontal Sync Start Register<br>CR5: Horizontal Sync End Register<br>CR6: Vertical Total Register<br>CR7: Overflow Register<br>CR8: Screen A Preset Row Scan Register<br>CR9: Character Cell Height Register<br>CR4: Text Cursor Start Register<br>CR6: Text Cursor End Register                                                                                                                                                                                                                                                                                                                                                                | 141<br>142<br>145<br>146<br>147<br>149<br>150<br>152<br>153<br>154<br>155<br>156<br>157<br>158                                                                                                                                                                                 |

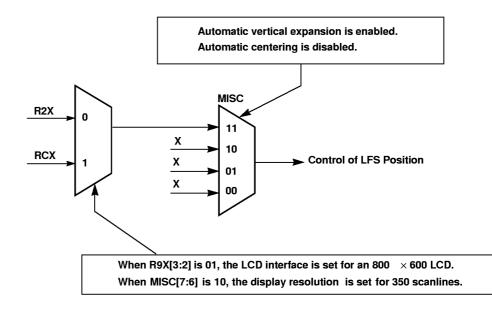

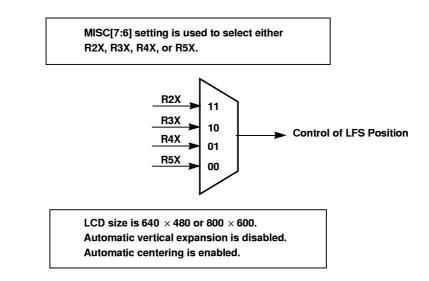

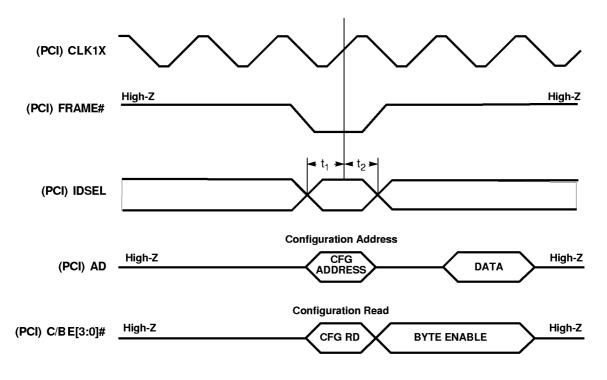

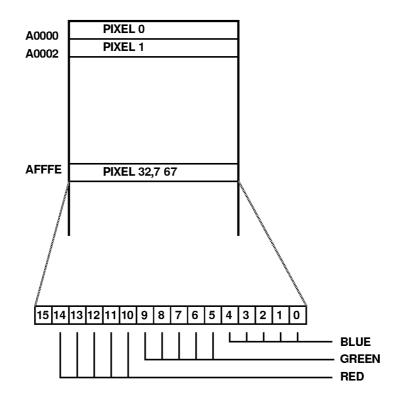

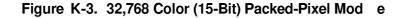

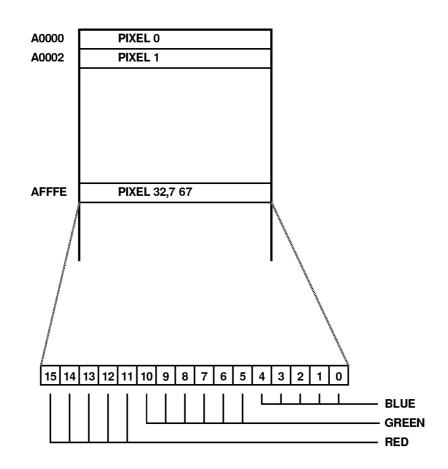

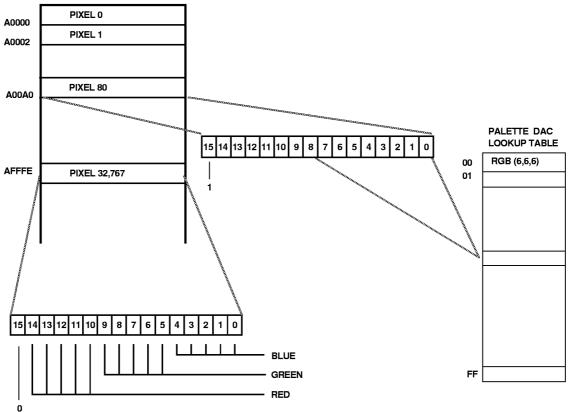

| 9. | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br>9.9<br>9.10<br>9.11<br>9.12<br>9.13<br>9.14                                                 | CRX: CRT Controller Index Register<br>CR0: Horizontal Total Register<br>CR1: Horizontal Display End Register<br>CR2: Horizontal Blanking Start Register<br>CR3: Horizontal Blanking End Register<br>CR4: Horizontal Sync Start Register<br>CR5: Horizontal Sync End Register<br>CR6: Vertical Total Register<br>CR7: Overflow Register<br>CR7: Overflow Register<br>CR8: Screen A Preset Row Scan Register<br>CR9: Character Cell Height Register<br>CR4: Text Cursor Start Register<br>CR8: Text Cursor End Register<br>CR6: Screen A Start Address High Register                                                                                                                                                                                                                                                                                         | <ul> <li>141</li> <li>142</li> <li>145</li> <li>146</li> <li>147</li> <li>149</li> <li>150</li> <li>152</li> <li>153</li> <li>154</li> <li>155</li> <li>156</li> <li>157</li> <li>158</li> <li>159</li> </ul>                                                                  |